앞서서 위에 언급한 내용들은 모두 코어 아키텍쳐의 하나의 코어에 해당되는 기술이다. 코어 아키텍쳐의 프로세서는 기본적으로 듀얼 코어로 구성되어 있으며 이후에 인텔이 보급형 프로세서 시장을 타겟으로 싱글 코어의 코어 아키텍쳐 프로세서도 내놓을 것으로 전망된 바 있지만 기본적으로 코어는 듀얼 코어 프로세서를 지향한다.

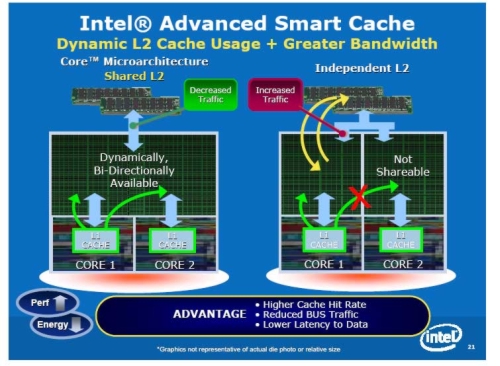

인텔이 최초로 발표했던 듀얼 코어 프로세서 펜티엄D의 경우 2개의 싱글 코어 프로세서 다이를 싱글 패키지로 묶은 것으로 사실상 2개의 프로세서 코어는 각기 고유의 캐쉬를 운용했으며 이 캐쉬 메모리는 상호 아무런 상관이 없었다. 그렇기 때문에 이 경우 각 코어의 캐쉬가 2MB이고 이것을 2x2MB=4MB라고 하는 것은 어불성설이나 다름 없으며 오히려 싱글 코어의 2MB 캐쉬보다 약간 더 나은 정도라고 보면 될 것이다.

이 경우 듀얼 코어에서 각 코어간의 캐쉬 정보가 공유되지 않으면 각 캐쉬는 같은 버스를 타고 각각 메모리에 접근해서 필요한 데이터를 가져 오려고 한다. 이 경우 FSB(Front Side Bus)는 당연히 트래픽이 늘어날 수 밖에 없다.

또한 캐쉬 효율성에서도 필요한 데이터가 다른 코어의 캐쉬에선 있는데 반대편 코어에서 없을 경우에는 같은 정보를 양쪽 캐쉬가 모두 보유하고 있어야 하는 낭비를 초래한다. 이는 비단 캐쉬 저장의 효율성을 떠나서도 어쨌든 양 회로가 모두 움직여야 한다는 기본적인 면에서 전력 소모량이 높을 수 밖에 없는 것이다.

인텔은 코어 듀오, 요나 프로세서에 최초로 양 코어가 하나의 L2 캐쉬를 공유하는 스마트 캐쉬를 도입한다. 양 코어는 하나의 대형 캐쉬를 공유해서 실질적으로 각 코어가 가용할 수 있는 캐쉬 용량도 커졌을 뿐만 아니라 캐쉬 데이터 중복의 낭비도 없애고 메모리 버스의 병목 현상도 줄였다. 인텔은 메모리 컨트롤러를 아직 프로세서 내부에 넣지 않아도 현재 FSB 구조가 충분하다고 보고 있는데, 아직까지는 메모리 버스가 성능을 가로막는 병목현상이 일어나는 곳이 아니라고 밝히고 있다. 즉 내장된 메모리 컨트롤러는 높은 대역폭을 제공하는 이점도 있지만 오히려 더 프로세서 내부의 캐쉬 알고리듬이 뛰어나면 병목 현상이 일어날 일이 없다고 주장했다.

코어 아키텍쳐에서는 이보다 개선된 "어드밴스드 스마트 캐쉬(Advanced Smart Cache)"를 도입했다. 이 것은 요나의 공유 캐쉬와 기본적으로 같지만 전력 관리 부분이 더 개선되었고 데이터를 필요 이전에 가져오기 위한 프리페치(Pre-Fetch) 알고리듬도 개선되었으며 데이터공유 효율도 높아졌다고 인텔은 밝혔다.

안에서 새는 바가지부터 막자

코어 아키텍쳐가 모바일 프로세서인 요나에서 많은 부분을 승계했다는 것은 곧 전력 관리 기술도 아예 아키텍쳐 개발 초기부터 염두에 두고 개발되었다는 것과 일맥상통한다.

일반적으로 인텔의 전력 관리 기술은 프로세서에 부하가 적을 시에 클럭을 낮춰 전력 소모량을 줄이는 스피드스텝과 같은 프로세서 전체를 보는 거시적인 관점에서 기술로 시작했지만 코어 아키텍쳐에서는 전력 관리 기능이 이에서 미시적인 관점으로 더 확대하고 파고 들어 프로세서를 구성하는 유닛 하나하나에도 전력 관리 기술을 적용시켰다. 코어 아키텍쳐가 완전히 백지에서부터 다시 설계되었다는 것은 아마도 전력 관리 기술 부분에 있어 회로 하나하나에도 세심히 신경을 썼다는 의미로 보아도 좋을 것이다.

코어 아키텍쳐에는 다이상에 디지털 온도 센서를 구비하고 있으며 이 센서는 물론 과도한 전력 소모와 발열을 감지하고 해당 부분의 동작 여부를 판단하는 잣대로 사용하도록 되어 있다. 이것에서 한가지 흥미로운 것은 만약 발열에 있어 여유가 있으면 오히려 역으로 프로세서의 클럭을 끌어올린다는 것. 쉽게 이야기하면 자동 오버클럭이라는 이야기인데, 물론 이것은 아직 인텔이 정식 확인한 바는 아니며 프로세서 업계에서 도는 이야기정도에 불과하다.

코어 아키텍쳐의 듀얼 코어 프로세서에서 각 코어는 각각 독립적으로 전력 관리 기능을 수행한다. 즉 하나의 코어만이 필요한 작업에서는 나머지 하나 코어의 전력 소모량을 떨어뜨리는 것. 여기서 끝나지 않고 인텔은 코어 내부의 대부분의 버스에도 전력 소모 통제를 위한 일종의 게이트를 설치해 놓았다. 즉 특정 유닛으로 통하는 버스가 일정 시간 동안 트래픽이 없거나 낮을 경우에는 이 버스를 슬립 모드로 동작시킨다. 일례로 128비트 연산이 가능한 부동 소수 연산 유닛에서 만약 대부분의 연산데이터가 64비트라면 이 버스의 절반을 꺼버리는 것이다. 인텔이 이번 프로세서 아키텍쳐 개발시 얼마나 전력 관리 소모량에 신경을 썼나 엿볼 수 있는 부분이며 동시에 이전 프로세서가 많은 두통을 인텔에게 주었다는 것을 반증하는 것이기도 하다.